# **TECHNICAL REPORT • OPEN ACCESS**

# The DAQ system of the 12,000 channel CMS high granularity calorimeter prototype

To cite this article: on behalf of the CMS HGCAL collaboration et al 2021 JINST 16 T04001

View the article online for updates and enhancements.

This content was downloaded from IP address 106.203.26.246 on 07/08/2021 at 10:02

PUBLISHED BY IOP PUBLISHING FOR SISSA MEDIALAB

RECEIVED: December 2, 2020 ACCEPTED: February 2, 2021 PUBLISHED: April 15, 2021

TECHNICAL REPORT

# The DAQ system of the 12,000 channel CMS high granularity calorimeter prototype

B. Acar,<sup>c</sup> G. Adamov,<sup>b</sup> C. Adloff,<sup>ag</sup> S. Afanasiev,<sup>x</sup> N. Akchurin,<sup>ao</sup> B. Akgün,<sup>c,e,\*</sup> M. Alhusseini,<sup>w</sup> J. Alison,<sup>f</sup> G. Altopp,<sup>d</sup> M. Alyari,<sup>i</sup> S. An,<sup>f</sup> S. Anagul,<sup>g</sup> I. Andreev,<sup>v</sup> M. Andrews,<sup>f</sup> P. Aspell,<sup>e</sup> I.A. Atakisi,<sup>c</sup> O. Bach,<sup>h</sup> A. Baden,<sup>ab</sup> G. Bakas,<sup>ah</sup> A. Bakshi,<sup>i</sup> S. Banerjee,<sup>*i*</sup> P. Bargassa,<sup>*z*</sup> D. Barney,<sup>*e*</sup> E. Becheva,<sup>*aa*</sup> P. Behera,<sup>*r*</sup> A. Belloni,<sup>*ab*</sup> T. Bergauer,<sup>*l*</sup> M. Besancon,<sup>al</sup> S. Bhattacharya,<sup>ae</sup> S. Bhattacharya,<sup>am</sup> D. Bhowmik,<sup>am</sup> P. Bloch,<sup>s</sup> A. Bodek,<sup>*ak*</sup> G. Bombardi,<sup>*e*</sup> M. Bonanomi,<sup>*aa*</sup> A. Bonnemaison,<sup>*aa*</sup> S. Bonomally,<sup>*s*</sup> J. Borg,<sup>*s*</sup> F. Bouyjou,<sup>al</sup> D. Braga,<sup>i</sup> J. Brashear,<sup>ac</sup> E. Brondolin,<sup>e</sup> P. Bryant,<sup>f</sup> J. Bueghly,<sup>ae</sup> B. Bilki,<sup>w</sup> B. Burkle,<sup>d</sup> A. Butler-Nalin,<sup>ap</sup> S. Callier,<sup>aj</sup> D. Calvet,<sup>al</sup> X. Cao,<sup>n</sup> B. Caraway,<sup>a</sup> S. Caregari,<sup>ag</sup> L. Ceard,<sup>*ai*</sup> Y.C. Cekmecelioglu,<sup>*c*</sup> S. Cerci,<sup>*t*</sup> G. Cerminara,<sup>*e*</sup> N. Charitonidis,<sup>*e*</sup> R. Chatterjee,<sup>*ac*</sup> Y.M. Chen,<sup>ab</sup> Z. Chen,<sup>ae</sup> K.y. Cheng,<sup>ag</sup> S. Chernichenko,<sup>o</sup> H. Cheung,<sup>i</sup> C.H. Chien,<sup>ai</sup> S. Choudhury,<sup>p</sup> D. Čoko,<sup>j</sup> G. Collura,<sup>ap</sup> F. Couderc,<sup>al</sup> L. Cristella,<sup>e</sup> I. Dumanoglu,<sup>g</sup> D. Dannheim,<sup>e</sup> P. Dauncey,<sup>s</sup> A. David,<sup>e</sup> G. Davies,<sup>s</sup> E. Day,<sup>f</sup> P. DeBarbaro,<sup>ak</sup> F. De Guio,<sup>ao</sup> C. de La Taille,<sup>*aj*</sup> M. De Silva,<sup>*h*</sup> P. Debbins,<sup>*w*</sup> E. Delagnes,<sup>*al*</sup> J.M. Deltoro,<sup>*e*</sup> G. Derylo,<sup>*i*</sup> P.G. Dias de Almeida,<sup>e</sup> D. Diaz,<sup>m</sup> P. Dinaucourt,<sup>aj</sup> J. Dittmann,<sup>a</sup> M. Dragicevic,<sup>l</sup> S. Dugad,<sup>an</sup> V. Dutta, *ap* S. Dutta, *am* J. Eckdahl, *ap* T.K. Edberg, *b* M. El Berni, *j* S.C. Eno, *b* Yu. Ershov, *x* P. Everaerts,<sup>s</sup> S. Extier,<sup>aj</sup> F. Fahim,<sup>i</sup> C. Fallon,<sup>ak</sup> S. Fiorendi,<sup>e</sup> B.A. Fontana Santos Alves,<sup>e</sup> E. Frahm,<sup>ac</sup> G. Franzoni,<sup>e</sup> J. Freeman,<sup>i</sup> T. French,<sup>e</sup> Y. Guler,<sup>g</sup> E. Gurpinar Guler,<sup>g</sup> M. Gagnan,<sup>an</sup> P. Gandhi,<sup>i</sup> S. Ganjour,<sup>al</sup> A. Garcia-Bellido,<sup>ak</sup> Z. Gecse,<sup>i</sup> Y. Geerebaert,<sup>aa</sup> H. Gerwig,<sup>e</sup> O. Gevin,<sup>al</sup> A. Gilbert,<sup>ae</sup> W. Gilbert,<sup>ac</sup> K. Gill,<sup>e</sup> C. Gingu,<sup>i</sup> S. Gninenko,<sup>v</sup> A. Golunov,<sup>x</sup> I. Golutvin,<sup>x</sup> T. Gonzalez,<sup>ap</sup> N. Gorbounov,<sup>x</sup> L. Gouskos,<sup>e</sup> Y. Gu,<sup>n</sup> F. Guilloux,<sup>al</sup> E. Gülmez,<sup>c</sup> E. Hamamci,<sup>c</sup> M. Hammer,<sup>i</sup> A. Harilal,<sup>f</sup> K. Hatakeyama,<sup>a</sup> A. Heering,<sup>af</sup> V. Hegde, ao U. Heintz, V. Hinger, N. Hinton, J. Hirschauer, J. Hoff, W.S. Hou, ai C. Isik, J. Incandela,  $a^{ap}$  A. Irshad,  $e^{e}$  S. Jain,  $a^{c}$  H.R. Jheng,  $a^{g}$  U. Joshi,  $i^{i}$  O. Kara,  $g^{g}$  V. Kachanov,  $o^{o}$ A. Kalinin,<sup>o</sup> R. Kameshwar,<sup>an</sup> A. Kaminskiy,<sup>ad</sup> H. Kanso,<sup>y</sup> A. Karneyeu,<sup>v</sup> O. Kaya,<sup>c</sup> M. Kaya,<sup>c</sup> A. Khukhunaishvili,<sup>ak</sup> J. Kieseler,<sup>e</sup> S. Kim,<sup>m</sup> K. Koetz,<sup>m</sup> T. Kolberg,<sup>m</sup> A. Kristić,<sup>j</sup> M. Krohn,<sup>ac</sup> K. Krüger,<sup>h</sup> N. Kulagin,<sup>o</sup> S. Kulis,<sup>e</sup> S. Kunori,<sup>ao</sup> C.M. Kuo,<sup>ag</sup> V. Kuryatkov,<sup>ao</sup> S. Kyre,<sup>*ap*</sup> O.K. Köseyan,<sup>*w*</sup> Y. Lai,<sup>*ab*</sup> K. Lamichhane,<sup>*ao*</sup> G. Landsberg,<sup>*d*</sup> C. Lange,<sup>*e*</sup> J. Langford,<sup>s</sup> M.Y. Lee,<sup>ag</sup> E. Leogrande,<sup>e</sup> A. Levin,<sup>o</sup> J.H. Li,<sup>ai</sup> A. Li,<sup>ap</sup> B. Li,<sup>n</sup> H. Liao,<sup>n</sup> D. Lincoln,<sup>*i*</sup> L. Linssen,<sup>*e*</sup> R. Lipton,<sup>*i*</sup> Y. Liu,<sup>*n*</sup> A. Lobanov,<sup>*aa*</sup> K. Long,<sup>*e*</sup> R.S. Lu,<sup>*ai*</sup> I. Lysova,<sup>*v*</sup> A.M. Magnan,<sup>s</sup> F. Magniette,<sup>aa</sup> A.A. Maier,<sup>e</sup> A. Malakhov,<sup>x</sup> I. Mandjavize,<sup>al</sup> M. Mannelli,<sup>e</sup>

© 2021 CERN for the benefit of the CMS collaboration. Published by IOP Publishing Ltd on behalf of Sissa Medialab. Original content from this work may be used under the terms of the Creative Commons Attribution 4.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

J. Mans, ac A. Marchioro, A. Martelli, P. Masterson, B. Meng, T. Mengke, ac E. Meschi, e A. Mestvirishvili,<sup>w</sup> I. Mirza,<sup>an</sup> S. Moccia,<sup>e</sup> I. Morrissey,<sup>ac</sup> T. Mudholkar,<sup>f</sup> J. Musić,<sup>j</sup> Y. Musienko,<sup>af</sup> S. Nabili,<sup>ab</sup> A. Nagar,<sup>ap</sup> A. Nikitenko,<sup>u</sup> D. Noonan,<sup>k</sup> M. Noy,<sup>e</sup> K. Nurdan,<sup>c</sup> C. Ochando,<sup>aa</sup> B. Odegard,<sup>ap</sup> N. Odell,<sup>ae</sup> Y. Onel,<sup>w</sup> W. Ortez,<sup>ap</sup> J. Ozegović,<sup>j</sup> S. Ozkorucuklu,<sup>*t*</sup> L. Pacheco-Rodriguez,<sup>*aa*</sup> E. Paganis,<sup>*ai*</sup> D. Pagenkopf,<sup>*ap*</sup> V. Palladino,<sup>*s*</sup> S. Pandey,<sup>q</sup> F. Pantaleo,<sup>e</sup> C. Papageorgakis,<sup>ab</sup> I. Papakrivopoulos,<sup>ah</sup> J. Parshook,<sup>f</sup> N. Pastika,<sup>a</sup> M. Paulini,<sup>f</sup> P. Paulitsch,<sup>l</sup> T. Peltola,<sup>ao</sup> R. Pereira Gomes,<sup>e</sup> H. Perkins,<sup>e</sup> P. Petiot,<sup>e</sup> M. Pierini,<sup>e</sup> F. Pitters,<sup>e</sup> F. Pitters,<sup>1</sup> H. Prosper,<sup>m</sup> M. Prvan,<sup>j</sup> I. Puljak,<sup>j</sup> S.R. Qasim,<sup>e</sup> H. Qu,<sup>e</sup> T. Quast,<sup>e</sup> R. Quinn,<sup>ac</sup> M. Quinnan,<sup>ap</sup> K. Rapacz,<sup>e</sup> L. Raux,<sup>aj</sup> G. Reichenbach,<sup>ac</sup> M. Reinecke,<sup>h</sup> M. Revering,<sup>ac</sup> M. Rieger,<sup>e</sup> A. Rodriguez,<sup>e</sup> T. Romanteau,<sup>aa</sup> A. Rose,<sup>s</sup> M. Rovere,<sup>e</sup> A. Roy,<sup>ag</sup> P. Rubinov,<sup>i</sup> R. Rusack,<sup>ac</sup> A.E. Simsek,<sup>g</sup> U. Sozbilir,<sup>g</sup> O.M. Sahin,<sup>al</sup> A. Sanchez, R. Saradhy, ac T. Sarkar, ag M.A. Sarkisla, J.B. Sauvan, ad I. Schmidt, w M. Schmitt,<sup>ae</sup> E. Scott,<sup>s</sup> C. Seez,<sup>s</sup> F. Sefkow,<sup>h</sup> M. Selvaggi,<sup>e</sup> S. Sharma,<sup>q</sup> I. Shein,<sup>o</sup> A. Shenai,<sup>*i*</sup> R. Shukla,<sup>*an*</sup> E. Sicking,<sup>*e*</sup> P. Sieberer,<sup>*e*</sup> Y. Sirois,<sup>*aa*</sup> V. Smirnov,<sup>*x*</sup> E. Spencer,<sup>*d*</sup> A. Steen,<sup>ai</sup> J. Strait,<sup>i</sup> T. Strebler,<sup>s</sup> N. Strobbe,<sup>ac</sup> J.W. Su,<sup>ai</sup> E. Sukhov,<sup>x</sup> M. Sun,<sup>f</sup> L. Sun,<sup>n</sup> D. Sunar Cerci,<sup>t</sup> A. Surkov,<sup>o</sup> C. Syal,<sup>i</sup> B. Tali,<sup>g</sup> U.G. Tok,<sup>g</sup> A. Kayis Topaksu,<sup>g</sup> C.L. Tan,<sup>ak</sup> I. Tastan,<sup>c</sup> T. Tatli,<sup>c</sup> R. Thaus,<sup>ak</sup> S. Tekten,<sup>c</sup> D. Thienpont,<sup>aj</sup> T. Pierre-Emile,<sup>aa</sup> E. Tiras,<sup>w</sup> M. Titov, <sup>al</sup> D. Tlisov, <sup>v</sup> J. Troska,<sup>e</sup> Z. Tsamalaidze,<sup>b</sup> G. Tsipolitis,<sup>ah</sup> A. Tsirou,<sup>e</sup> N. Tyurin,<sup>o</sup> S. Undleeb, *ao* D. Urbanski, *ac* V. Ustinov, *x* A. Uzunian, *o* G.P. Van Onsem, *e* M. van de Klundert,<sup>h</sup> J. Varela,<sup>z</sup> M. Velasco,<sup>ae</sup> T. Vergine,<sup>e</sup> M. Vicente Barreto Pinto,<sup>e</sup> P.M. da Silva,<sup>e</sup> T. Virdee,<sup>s</sup> R. Vizinho de Oliveira,<sup>e</sup> J. Voelker,<sup>d</sup> E. Voirin,<sup>i</sup> Z. Wang,<sup>ao</sup> X. Wang,<sup>*i*</sup> F. Wang,<sup>*n*</sup> M. Wayne,<sup>*af*</sup> S.N. Webb,<sup>*s*</sup> M. Weinberg,<sup>*f*</sup> A. Whitbeck,<sup>*ao*</sup> D. White,<sup>*ap*</sup> R. Wickwire,<sup>*i*</sup> J.S. Wilson,<sup>*a*</sup> D. Winter,<sup>*e*</sup> H.Y. Wu,<sup>*ai*</sup> L. Wu,<sup>*n*</sup> C. H Yeh,<sup>*ag*</sup> R. Yohay,<sup>*m*</sup> D. Yu,<sup>*d*</sup> S.S. Yu,<sup>ag</sup> G.B. Yu,<sup>al</sup> F. Yumiceva,<sup>k</sup> A. Zacharopoulou,<sup>ah</sup> N. Zamiatin,<sup>x</sup> A. Zarubin,<sup>x</sup> S. Zenz,<sup>s</sup> J. Zhang<sup>m</sup> and H. Zhang<sup>n</sup> on behalf of the CMS HGCAL collaboration

- <sup>b</sup>Georgian Technical University, 77 Kostava Str, Tbilisi, GE 0175, U.S.A.

- <sup>c</sup>Bogazici University, Bebek 34342, Istanbul, Turkey

- <sup>d</sup>Brown University, 182 Hope Street, Providence, RI 02912, U.S.A.

- <sup>e</sup>CERN, Esplanade des Particules 1, Geneve 23 1211, Switzerland

- <sup>f</sup> Carnegie Mellon University, 5000 Forbes Ave, Pittsburgh, PA 15213, U.S.A.

- <sup>g</sup>Cukurova University, Adana 01330, Turkey

- <sup>h</sup>Deutsches Elektronen-Synchrotron DESY,

- Notkestrasse 85, Hamburg 22607, Germany

- <sup>i</sup> Fermi National Accelerator Laboratory, P.O. Box 500, Batavia, IL 60510, U.S.A.

- <sup>j</sup> University of Split, Faculty of Electrical Engineering, Mechanical Engineering and Naval Architecture,

- R. Boškovića 32, Split, Croatia

- <sup>k</sup> Florida Institute of Technology, 150 W University Blvd, Melbourne, FL 32901, U.S.A.

- <sup>1</sup>HEPHY Viena, Nikolsdorfergasse 18, Vienna 1050, Austria

- <sup>m</sup>Florida State University, 600 W. College Ave., Tallahassee, FL 32306, U.S.A.

- <sup>n</sup>IHEP Beijing, 19 Yuquan Road, Shijing Shan, China

- <sup>o</sup>IHEP Protvino, Protvino 142281, Russia

<sup>&</sup>lt;sup>a</sup>Baylor University, Waco, TX 76706, U.S.A.

<sup>\*</sup>Corresponding author.

<sup>p</sup>Indian Institute of Science, Bangalore, India <sup>q</sup>Indian Institute of Science Education and Research, Dr. Homi Bhabha Road, Pune 411008, India <sup>r</sup> Indian Institute of Technology, Chennai 60036, India <sup>s</sup>Imperial College, Prince Consort Road, London SW7 2AZ, U.K. <sup>t</sup>Istanbul University, Vezneciler-Fatih, Istanbul 34134, Turkey <sup>u</sup>ITEP Moscow, B. Cheremushkinskaya ulitsa 25, Moscow 117 259, Russia <sup>v</sup>Institute for Nuclear Research of Russian Academy of Science, 60th Oct. Anniversary prospekt 7A, Moscow 117 312, Russia <sup>w</sup> The University of Iowa, 203 Van Allen Hall, Iowa City, IA 52242, U.S.A. <sup>x</sup>International Intergovernmental Organization Joint Institute for Nuclear Research JINR, 6 Joliot-Curie St, Dubna, Moscow 141980, Russia <sup>y</sup>The Lebanese University, Department of Physics, P.O. Box 6573/14 Badaro, Museum, Beirut, Lebanon <sup>z</sup>LIP, Avenida Prof. Gama Pinto, No. 2, Lisbon 1649-003, Portugal <sup>aa</sup>Laboratoire Leprince-Ringuet CNRS/IN2P3, Route de Saclay, Ecole Polytechnique 91128, France <sup>ab</sup> The University of Maryland, College Park, MD 20742, U.S.A. ac The University of Minnesota, 116 Church Street SE, Minneapolis, MN 55405, U.S.A. <sup>ad</sup> M.V. Lomonosov Moscow State University (MSU Moscow), 1/2, Leninskie gory, Moscow 119 991, Russia ae Northwestern University, 2145 Sheridan Rd, Evanston, IL 60208, U.S.A. af University of Notre Dame, Notre Dame, IN 46556, U.S.A. <sup>ag</sup>National Central University Taipei (NCU), No. 300, Jhongda Rd, Jhongli City 32001, Taiwan <sup>ah</sup>National Technical University of Athens, 9, Heroon Polytechneiou Street, Athens 15780, Greece ai National Taiwan University, Taipei 10617, Taiwan <sup>a j</sup> Laboratoire OMEGA CNRS/IN2P3, Ecole Polytechnique, Route de Saclay, Palaiseau 91128, France ak University of Rochester, Campus Box 270171, Rochester, NY 14627, U.S.A. al CEA Paris-Saclay, IRFU, Batiment 141, Gif-Sur-Yvette 91191, Paris, France <sup>am</sup>SINP, Sector 1 Block AF, Bidhan Nagar, Kolkata 700 064, India <sup>an</sup>Tata Institute of Fundamental Research, Homi Bhabha Road, Mumbai 400 005, India ao Texas Tech University, Lubbock, TX 79409, U.S.A. <sup>ap</sup>UC Santa Barbara, Santa Barbara, CA 93106, U.S.A.

*E-mail:* Bora.Akgun@cern.ch, Roger.Rusack@cern.ch

ABSTRACT: The CMS experiment at the CERN LHC will be upgraded to accommodate the 5-fold increase in the instantaneous luminosity expected at the High-Luminosity LHC (HL-LHC) [1]. Concomitant with this increase will be an increase in the number of interactions in each bunch crossing and a significant increase in the total ionising dose and fluence. One part of this upgrade is the replacement of the current endcap calorimeters with a high granularity sampling calorimeter equipped with silicon sensors, designed to manage the high collision rates [2]. As part of the development of this calorimeter, a series of beam tests have been conducted with different sampling configurations using prototype segmented silicon detectors. In the most recent of these tests, conducted in late 2018 at the CERN SPS, the performance of a prototype calorimeter equipped with  $\approx 12,000$  channels of silicon sensors was studied with beams of high-energy electrons, pions and muons. This paper describes the custom-built scalable data acquisition system that was built with readily available FPGA mezzanines and low-cost Raspberry Pi computers.

KEYWORDS: Calorimeters; Data acquisition concepts

ArXiv ePrint: 2012.03876

# Contents

| 1 | Introduction                                          | ]  |  |  |  |  |  |  |  |  |

|---|-------------------------------------------------------|----|--|--|--|--|--|--|--|--|

| 2 | DAQ system architecture                               |    |  |  |  |  |  |  |  |  |

| 3 | Data format and back-end DAQ components               | 4  |  |  |  |  |  |  |  |  |

|   | 3.1 Skiroc2-CMS ASIC and prototype module data format | 2  |  |  |  |  |  |  |  |  |

|   | 3.2 Back-end DAQ electronics                          | 6  |  |  |  |  |  |  |  |  |

|   | 3.2.1 Readout board                                   | 6  |  |  |  |  |  |  |  |  |

|   | 3.2.2 Sync board                                      | ç  |  |  |  |  |  |  |  |  |

| 4 | Data acquisition software                             |    |  |  |  |  |  |  |  |  |

|   | 4.1 CMS-CE EUDAQ framework                            | 10 |  |  |  |  |  |  |  |  |

|   | 4.1.1 EUDAQ online data monitoring                    | 12 |  |  |  |  |  |  |  |  |

|   | 4.1.2 Data unpacking and first analysis steps         | 12 |  |  |  |  |  |  |  |  |

| 5 | System synchronization                                | 13 |  |  |  |  |  |  |  |  |

|   | 5.1 Beam-characterization detectors                   | 13 |  |  |  |  |  |  |  |  |

|   | 5.2 AHCAL                                             | 13 |  |  |  |  |  |  |  |  |

| 6 | Collected data                                        | 15 |  |  |  |  |  |  |  |  |

| 7 | Summary                                               | 15 |  |  |  |  |  |  |  |  |

# 1 Introduction

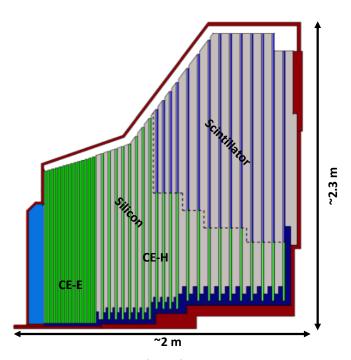

The HL-LHC at CERN is planned to operate with an instantaneous luminosity of  $5 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> or higher, delivering up to ten times more integrated luminosity than is expected in the current LHC programme. This increase poses significant challenges in the design and operation of the detectors at the HL-LHC. In particular, in the forward direction the absorbed dose will increase to as much as 2 MGy and the fluence in the innermost region is expected to reach  $10^{16} n_{eq}/cm^2$ , which is an unprecedented level in high energy collider experiments. Additionally there will be  $\approx 140$  protonproton interactions occurring (pile-up) in every bunch crossing, which happens at a rate of 40 MHz. This considerably complicates the reconstruction of events. To contend with these conditions, the CMS collaboration is planning a series of upgrades to some of the existing detector components, and replacing others with new detectors designed specifically to mitigate the effect of the high pileup [1]. As part of this upgrade programme the current electromagnetic and hadronic calorimeters in the endcaps will be replaced with a new calorimeter, known as the 'High-Granularity Calorimeter' (HGCAL) [2]. This new sampling calorimeter (CE) will be sub-divided into two sections, the electromagnetic (CE-E) and the hadronic (CE-H), in an arrangement shown in figure 1. The CE-E will be equipped with silicon sensors, while the CE-H will be equipped with both silicon sensors and scintillator tiles read out directly with SiPMs. In the CE-H the silicon sensors will be at small radii, close to the beam where the radiation levels are highest, and scintillator tiles at the larger

Electromagnetic calorimeter (CE-E): Si, Cu/CuW/Pb absorbers, 28 layers, 25.5 X<sub>0</sub> & ~1.7  $\lambda$ Hadronic calorimeter (CE-H): Si & scintillator, steel absorbers, 22 layers, ~9.5  $\lambda$

radii. The absorber of CE-E will be a mixture of lead, copper and sintered copper-tungsten, while in CE-H the absorber plates will be stainless steel. The hexagonal silicon sensors will be subdivided into hexagonal cells with areas of  $\approx 1.1 \text{ cm}^2$  or  $0.5 \text{ cm}^2$ , with the sensors with smaller cells placed at small radii in the higher fluence region. The full calorimeter will be operated at  $-30^{\circ}$ C to reduce the dark current in the silicon sensors and in the SiPMs. There will be 28 sampling layers in CE-E and 22 in CE-H. This high-transverse granularity, combined with the high longitudinal segmentation of the calorimeter has been selected, within the constraints of cost and available space, to optimise the identification and measurement of hadronic and electromagnetic showers in the presence of the high pile-up.

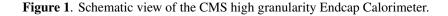

The basic detector unit is a silicon module. A module consists of a silicon sensor, glued to a baseplate on one side and to a printed circuit board (PCB) for the readout on the opposite side. The individual cells of the sensor are connected electrically to a readout ASIC on the PCB with wire-bonds that pass through holes in the PCB. The ASIC amplifies and digitises the analogue signals and transmits them to the off-detector electronics on receipt of an external trigger signal. By 2018 more than 100 prototype silicon modules have been produced using 6-inch hexagonal silicon sensors subdivided into cells with areas of  $\approx 1.1 \text{ cm}^2$ . A module is shown in figure 2 (left). Further details of the construction and assembly of the silicon modules used in these tests may be found in [3]. The modules were assembled into a prototype of HGCAL that was tested with beams of electrons, pions and muons at the CERN SPS.

The ASIC used to read out of the signals from the silicon cells was the Skiroc2-CMS [4], a custom ASIC designed by the OMEGA group at Ecole Polytechnique. The function of this 64-

channel ASIC was to measure both the amplitude of the signal and its time of arrival, so not only the energy response can be measured, but the timing performance can be characterised. This Skiroc2-CMS ASIC has many of the features of the HGCAL front-end readout ASIC in development.

In the latest beam test in late 2018 the HGCAL prototype was equipped with 94-hexagonal silicon modules arranged into a 26 radiation length electromagnetic section and a 5 nuclear interaction length hadronic section. Behind the prototype calorimeter we placed the Analog Hadronic Calorimeter (AHCAL) prototype, developed by the CALICE collaboration [5]. This calorimeter is a scintillator-based sampling calorimeter, similar in design to the proposed design of the HGCAL [2], but with much finer longitudinal segmentation. In the final test at the CERN SPS, data were taken with beams of muons, charged hadrons and electrons with energies ranging from 20 to 300 GeV at the H2 beam line of the CERN-SPS over a period of two weeks in October 2018.

The data acquisition (DAQ) system for the beam tests needed to be flexible and scalable to control and read out the increasing number of prototype silicon modules as they became available. It was designed with readily available FPGA mezzanines and low-cost Raspberry Pis, and scaled up to work with  $\approx$ 12,000 channels for the final test.

This paper describes the DAQ system and is structured as follows: the overall architecture of the system is described in section 2; the data format and the back-end DAQ components are described in section 3; the DAQ software is explained in section 4; in section 5 the detector systems used for system synchronisation is discussed and the operational experience is discussed in section 6.

#### 2 DAQ system architecture

Each hexagonal cell of the silicon sensor was connected to the 64-channel Skiroc2-CMS ASIC. Each channel of this ASIC had a low noise pre-amplifier followed by high- and low-gain shapers, with a shaping time of 40 ns. Both of the shapers had analogue-to-digital converters (ADCs) that sampled the signal every 25 ns. The pre-amplifiers are also followed by time-over-threshold (ToT) and time-of-arrival (ToA) circuits. The ToT circuit measures the large amplitude signals (>600 fC) and the ToA circuit measures the arrival time of the signals with a precision of 50 ps. Further details of the design can be found in [4].

To simplify routing of the signals in a very dense board, four Skiroc2-CMS ASICs were used to readout the 128 channels of each silicon sensor, leaving half of the channels unused. The PCB also had a MAX®10 field programmable gate array (FPGA) to control the readout of the module. It received the clock, trigger and busy signals from the off-detector electronics, aggregated the data from the Skiroc2-CMS ASICs and transmitted it to the off-detector electronics. Figure 2 (left) is a photograph of a prototype module, with the Skiroc2-CMS ASICs marked with rectangles, and the MAX®10 FPGA, on the top left, indicated with a white circle.

Each of the prototype silicon modules was connected to the off-detector DAQ boards through an interposer board. These boards regulated the 5 V output from the DAQ boards to the 3.3 V needed by the prototype modules via HDMI cables. They also filtered and transmitted the bias voltage coming from the DAQ boards through RG174 cables to wires soldered to the prototype modules. A photograph of an interposer board is shown in figure 2 (right).

The off-detector electronics consisted of a set of custom 9U readout boards, described in section 3.2.1, each of which could receive data from up to eight silicon modules. All the readout

**Figure 2**. (Left) A prototype module used in beam tests. The Skiroc2-CMS ASICs are marked with white rectangles. The MAX®10 FPGA is marked with a white circle. The red grounding wire (on the left side) and, red and violet bias wires (on the right side) are soldered on the PCB. The micro HDMI (uHDMI) cable is connected on the top. (Right) An interposer board used in beam tests. The HDMI cable and bias voltage wires, connecting the interposer board to the prototype module, are connected on the top. The HDMI and RG174 cables, connecting the interposer board to the DAQ board, are connected on the bottom.

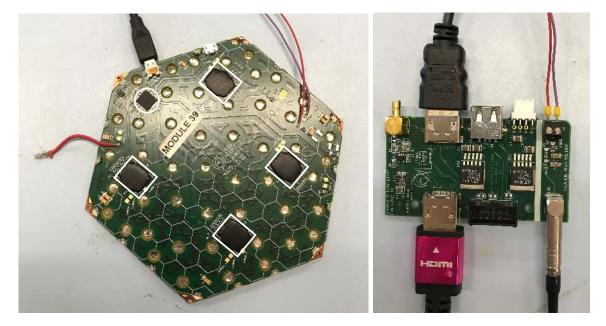

boards were synchronised by a single custom 9U synchronisation board, the 'sync board', described in section 3.2.2. The sync board distributed the clock, trigger and busy signals to all the readout boards. The readout boards communicated with the data acquisition computer through Ethernet, with a 100 Mbit/s output of the readout boards connected to a Gigabit Ethernet switch, from which data were sent to the DAQ computer for processing. In the tests with 94 silicon modules, one sync board and fourteen readout boards were mounted in two custom air-cooled crates. The crate that was equipped with one sync board and seven readout boards is shown in figure 3.

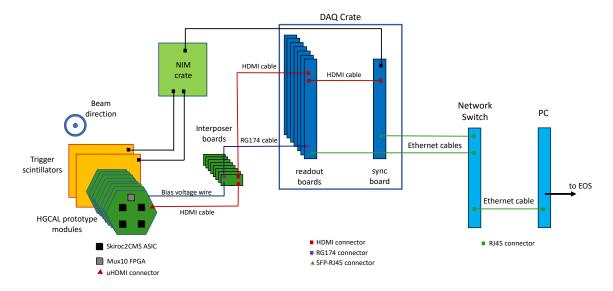

Figure 4 shows a schematic view of the inter-connectivity of the DAQ system. The readout boards were connected to the prototype silicon modules by HDMI cables both between the readout boards and the interposer boards and between the interposer boards and the modules. The trigger signal was formed from a coincidence of signals from two scintillation counters located upstream of the calorimeter. The 40 MHz system clock, generated on the sync board and the trigger signals were transmitted to the readout boards with HDMI cables. Since the beam was not synchronised with the clock, the trigger and the clock were asynchronous. The bias voltage was distributed to the silicon sensors through the readout boards with separate RG174 cables.

#### 3 Data format and back-end DAQ components

#### 3.1 Skiroc2-CMS ASIC and prototype module data format

In operation, the analog signals were stored every 25 ns in a switched-capacitor array (SCA) with a depth of 13 cells. When a trigger was received, the updating of the SCA was halted and the

**Figure 3**. A crate, used in HGCAL beam tests, populated with one sync board and seven readout boards. The sync board (in the leftmost slot) distributed the clock, trigger and busy signals to the readout boards via HDMI cables, not shown. The readout boards were used to send control data to the silicon modules, to receive data from them, and to transmit the data to the acquisition computer through an Ethernet switch (on the right side of the readout boards). The readout and sync boards were powered by the power modules located under the DAQ crate.

Figure 4. Schematic view of the DAQ system used in HGCAL beam tests.

two values for the ToA were stored, one referenced to the next falling edge of the 40 MHz clock, and the other to the next rising clock edge. Two values of the ToT were also kept, one with a fast ramp time-to-digital converter and another with a slow ramp. Figure 5 shows the data format of the Skiroc2-CMS ASIC.

When a trigger was received by the MAX®10 FPGA of the prototype silicon module (also referred to as hexaboard), the four Skiroc2-CMS ASICs converted the data in analogue memory to the digital data format. These data were then read out by the MAX®10 FPGA and packaged as shown in figure 6. The bits  $b_{Ai}$  belong to the ASIC "i" which followed the Skiroc2-CMS data format shown in figure 5. For every event 30784 bytes of data were transmitted from each hexaboard. These data were then gathered, via the HDMI-uHDMI cables, by the back-end readout boards.

# 3.2 Back-end DAQ electronics

The DAQ system was designed to be easily scalable to provide a readout for different numbers of silicon modules. To minimise costs, readily available commercial components were used. Additionally, optical receiver modules (oRMs) [6], recovered from the CMS level-1 trigger system after it was upgraded with faster electronics, were used. Each oRM was equipped with a Kintex-7 FPGA, 4.8 Mbits of block RAM, two 6.6 Gbit/s bi-directional serial ports, and a 128 Mbit FLASH memory for configuration. The connection from the Kintex-7 FPGA to the gigabit Ethernet switch was made with SFP to RJ-45 adapters.

## 3.2.1 Readout board

In the final beam test in October 2018, there were 94 silicon modules that were read out with 14 readout boards mounted in two racks, synchronised by a sync board. The readout boards performed the following tasks:

- Loading firmware on the Max®10 FPGAs and module initialisation and reset.

- Generating and distributing control signals for the prototype silicon modules.

|                                             | 0                                                                                                            | 1 | 2 | 3     | 4                           |                        |   |     |                     | 1 | 15 |                                                                          |  |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------|---|---|-------|-----------------------------|------------------------|---|-----|---------------------|---|----|--------------------------------------------------------------------------|--|

| ×64 channels                                | annels100 $H_A$ Low gain ADC (SCA0)                                                                          |   |   |       |                             |                        |   |     |                     |   |    |                                                                          |  |

| ×64 channels                                | channels  1  0  0 $H_A$ High gain ADC (SCA0)                                                                 |   |   |       |                             |                        |   |     |                     |   |    |                                                                          |  |

|                                             | ×13 SCA cells                                                                                                |   |   |       |                             |                        |   |     |                     |   |    |                                                                          |  |

| ×64 channels                                | 1                                                                                                            | 0 | 0 | $H_A$ |                             |                        | ] | Low | gain ADC (SCA12)    |   |    |                                                                          |  |

| ×64 channels                                | 1                                                                                                            | 0 | 0 | $H_A$ | $H_A$ High gain ADC (SCA12) |                        |   |     |                     |   |    |                                                                          |  |

| ×64 channels                                | 1                                                                                                            | 0 | 0 | $H_A$ |                             | ToA (stop falling clk) |   |     |                     |   |    |                                                                          |  |

| ×64 channels                                | 1                                                                                                            | 0 | 0 | $H_A$ |                             |                        |   | То  | A (stop rising clk) |   |    | $\begin{cases} 1924 \times 16\text{-bit} \\ \text{integers} \end{cases}$ |  |

| $\times$ 64 channels 1 0 0 $H_T$ ToT (fas   |                                                                                                              |   |   |       | ToT (fast ramp)             |                        |   |     |                     |   |    |                                                                          |  |

| $\times 64 \text{ channels}$ 1 0 0 $H_T$ To |                                                                                                              |   |   |       | ToT (slow ramp)             |                        |   |     |                     |   |    |                                                                          |  |

|                                             | 0 0 0 Roll position (13-bit)                                                                                 |   |   |       |                             |                        |   |     |                     |   |    |                                                                          |  |

|                                             | 0      0      Global timestamp MSB (14-bit)        0      0      0      Global timestamp LSB (12-bit)      0 |   |   |       |                             |                        |   |     |                     |   |    |                                                                          |  |

|                                             |                                                                                                              |   |   |       |                             |                        |   |     | 0                   |   |    |                                                                          |  |

|                                             | 1                                                                                                            | 1 | 0 | 0     | 0                           | 0                      | 0 | 0   | Chip ID (8-bit)     |   |    | J                                                                        |  |

**Figure 5**. Data format of the Skiroc2-CMS ASIC.  $H_A$  is the hit bit for ToA and is set to '1' when ToA is fired. Similarly,  $H_T$  is the hit bit for ToT and is set to '1' when ToT is fired. The 13-bit roll position is used to reorder the SCA cells in time.

| 0 |     |     | 3   | 4        |          |          | 7        |                        |

|---|-----|-----|-----|----------|----------|----------|----------|------------------------|

|   | HEA | DER |     |          | 1 bit pe | er ASIC  |          |                        |

| 1 | 0   | 0   | 0   | $b_{A0}$ | $b_{A1}$ | $b_{A2}$ | $b_{A3}$ |                        |

|   |     |     | • • | •        |          |          |          | $1924 \times 16$ bytes |

| 1 | 0   | 0   | 0   | $b_{A0}$ | $b_{A1}$ | $b_{A2}$ | $b_{A3}$ | J                      |

**Figure 6**. Hexaboard data format. The bits  $b_{Ai}$  belong to the ASIC "i" which followed the Skiroc2-CMS data format described by figure 5.

- Accumulating the data received from the prototype silicon modules.

- Distributing the clock, busy and trigger signals.

- Distributing the low voltage power and the bias voltage for the prototype silicon modules.

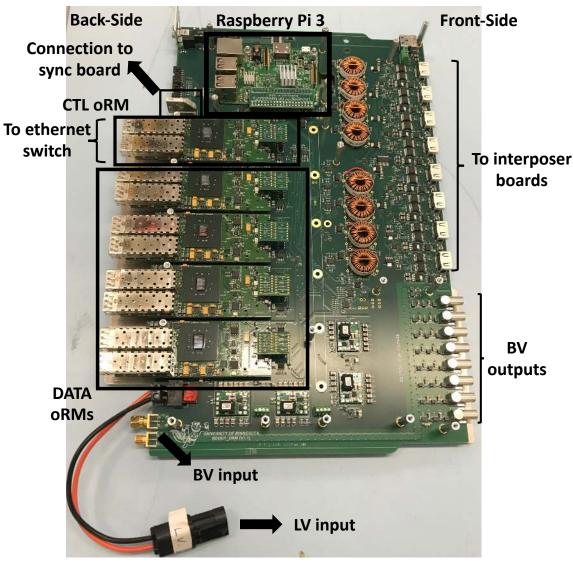

The readout board, shown in figure 7, was a custom PCB equipped with five oRMs and a Raspberry Pi 3 Model B. Each board had eight HDMI ports on the front panel connected to the silicon modules through the interposers and one HDMI port on the back panel for connection to the sync board. On the front of each board there were eight RG174 connectors that were used to distribute, after filtering, the bias voltage through the interposers to each detector module.

The overall readout cycle was controlled via helper processes running on the Raspberry Pi, which communicated with each oRM through the SPI bus. Each Raspberry Pi was connected to the

**Figure 7.** The readout board used to send control data to the silicon modules, to receive data from them and to transmit it to the data acquisition computer. It readout data from up to eight silicon modules via HDMI connectors. It also supplied the bias voltage for up to eight prototype silicon modules via standard RG174 connectors. It was equipped with one control and four data oRMs and one Raspberry Pi.

central DAQ server through its Ethernet port, from which it also received 'Start', 'Stop', and other commands.

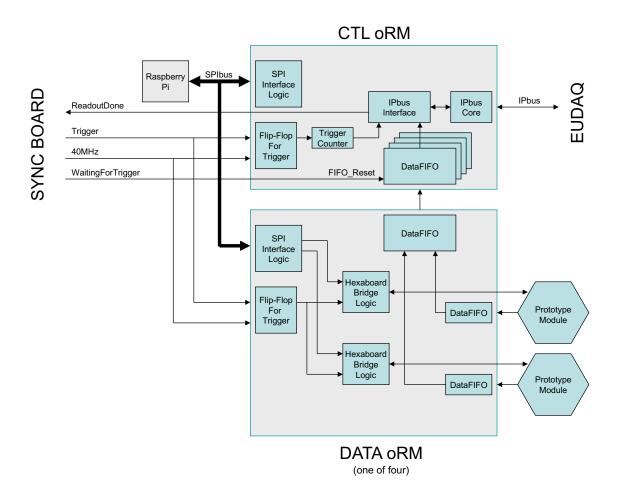

A single readout board was equipped with five oRMs: one control (CTL) oRM, and four DATA oRMs. The DATA oRMs were responsible for reading the data from up to two silicon modules, while the CTL oRM received data from the DATA oRMs and transferred it to the central server. It also managed the communication with the sync board. The firmware installed on the CTL oRM's FPGA included the IPBus package [7, 8] for these dual purposes. The IPBus IP and MAC addresses of the oRM were set by the Raspberry Pi, as well as other parameters used by the CTL oRM as it combined the four streams of data.

Before a run started, the helper processes on the Raspberry Pis first configured the ASICs on the prototype silicon modules, and data collection was initiated. The Trigger signal was broadcast from the sync board to the readout boards, from where it was forwarded on to the modules. After receiving the trigger signal, the helper processes running on the readout boards' Raspberry Pis prompted the ASICs to initiate data transmission. The data from the ASICs were then sent unprocessed, via the MAX®10 FPGA, to the DATA oRMs, where it was then merged into a single data stream by the CTL oRM. The 4-bit headers of figure 6 were then dropped and 32-bit integers were built with the data from up to eight modules, corresponding to 32 ASICs. These 32-bit integers were written to a FIFO to be readout by the central server using the IPBus protocol over a gigabit Ethernet link. When ready, a flag was set inside the CTL's RAM to indicate that the data were ready for transfer. In figure 8 the output data format of the CTL oRM FIFO is shown.

Once the data had been fully read out by the server, the helper processes on the Raspberry Pis reset the ASICs, and sent a start acquisition signal. The CTL oRM then sent a 'ReadoutDone' signal to the sync board, indicating the boards had finished their cycles and were ready to receive the next trigger. The firmware block diagram of the readout board is shown in figure 9.

| 0         | 1         | 2                       | 3                       | 4 |     | <br>27 | 28                      | 29                      | 30                      | 31                      |   |                            |

|-----------|-----------|-------------------------|-------------------------|---|-----|--------|-------------------------|-------------------------|-------------------------|-------------------------|---|----------------------------|

| $b_{0,0}$ | $b_{0,1}$ | <i>b</i> <sub>0,2</sub> | <i>b</i> <sub>0,3</sub> |   |     |        | <i>b</i> <sub>7,0</sub> | <i>b</i> <sub>7,1</sub> | <i>b</i> <sub>7,2</sub> | <i>b</i> <sub>7,3</sub> |   | 20704 22.1                 |

|           |           |                         |                         |   |     |        |                         |                         |                         |                         |   | 30784 × 32-bit<br>integers |

| $b_{0,0}$ | $b_{0,1}$ | <i>b</i> <sub>0,2</sub> | <i>b</i> <sub>0,3</sub> |   | ••• |        | <i>b</i> <sub>7,0</sub> | <i>b</i> <sub>7,1</sub> | <i>b</i> <sub>7,2</sub> | <i>b</i> <sub>7,3</sub> | ) | 0                          |

**Figure 8**. Data format of the CTL oRM FIFO readout by the central server using the IPBus protocol. The bits  $b_{i,j}$  correspond to the data of ASIC "j" of module "i".

#### 3.2.2 Sync board

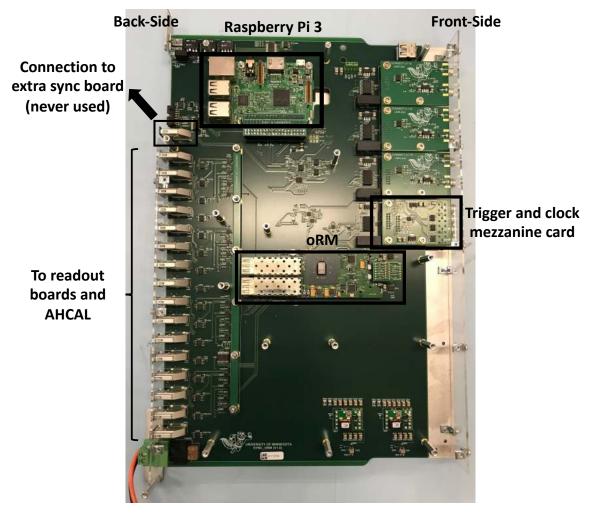

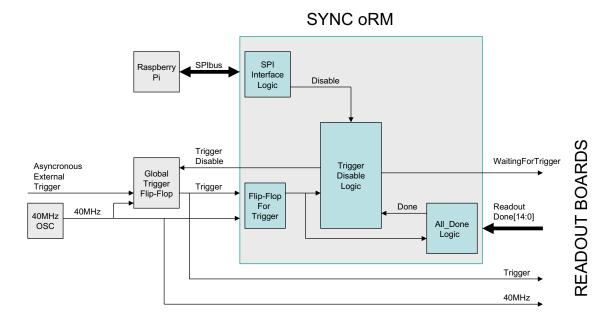

The function of the sync board, shown in figure 10, was the distribution of the common signals to the readout boards and to synchronise the flow of data from the readout boards. The sync board generated the 40 MHz system clock on a small mezzanine card mounted at the rear of the board. On the same mezzanine there were four  $50 \Omega$  RG174 connectors. Two were for the Trigger and Veto signal inputs and two for the Clock and a copy of the Trigger signal outputs. The Veto signal was not used in these tests. Processing on the sync boards was handled by a Raspberry Pi as well as a central (SYNC) oRM. One sync board could control up to 15 readout boards through 15 HDMI ports mounted on the front. An extra HDMI port was mounted on the front to allow for the possibility of daisy-chaining two or more sync boards together when more than 15 readout boards are to be readout.

At the start of a readout cycle, the sync board waited for an asynchronous External Trigger signal. Then this signal was synchronized with the on-board 40 MHz clock and sent to the readout boards to be distributed to the silicon modules. In parallel a 'busy' flag is asserted to prevent extra triggers until the readout of the event is completed. The 'busy' flag is de-asserted when the sync board received a 'ReadoutDone' signal from each readout board. Once this signal was received from all the readout boards, the sync board made itself ready to process the next available trigger. The firmware block diagram of the sync board is shown in figure 11.

Figure 9. The firmware block diagram of the readout board.

# 4 Data acquisition software

The DAQ software selected for these tests was based on the EUDAQ [9] framework. This framework, written in C++, was developed specifically for small-to-medium scale systems with significantly less overhead than frameworks used in large scale experiments, like XDAQ [10]. Additionally, in separate earlier tests of the AHCAL prototype, the EUDAQ system had already been used successfully.

The EUDAQ framework was designed to be modular and portable. It was structured so that software for the readout of specific detector components was kept separate and distinct from the core processes. For this each detector component that produced data had a 'Producer' process running. The functions performed by the Producer was to initialise, configure, issue stops and starts to the component, and to collect the data and forward it to the core process.

# 4.1 CMS-CE EUDAQ framework

A Readout Producer was developed to read out the data from one or more readout boards in parallel. During the combined beam test of October 2018, the DAQ had seven of these Readout Producers, each connected to two readout boards. The  $\mu$ TCA Hardware Access Library ( $\mu$ HAL) was used

**Figure 10**. The sync board was used to control up to 15 readout boards. It received the Veto and the Trigger signals and distributed control signals to up to 15 readout boards. On top of the 15 HDMI ports for readout board control there was one extra port for connection to another sync board for daisy-chaining. It was equipped with a Raspberry Pi and an Kintex-7 FPGA for control and communication. It was also equipped with a mezzanine card for clock generation and receiving external signals.

to read the IPBus UDP transactions from the readout boards. The sequence of operations of the Readout Producer were as follows:

- 1. Wait until each  $\mu$ HAL interface is notified that a trigger occurred (by checking an IPBus register of the CTL oRM boards).

- Read out the FIFO of the CTL oRM board from each readout board and fill raw data containers. The data format of this FIFO is described in section 3.2.1. A time-stamp — the number of 40 MHz clock cycles in a 64-bit integer since the last configuration — is read out with the data.

- 3. Create an event block containing the raw data from each readout board, the time-stamp of the readout board and the event ID.

Figure 11. The firmware block diagram of the sync board.

- 4. Forward the event block to the EUDAQ data collector.

- 5. Increment the event ID.

- 6. Return to step 1 and wait for the next trigger.

Once the readout was complete, data from each of the event blocks from each of the Readout Producers were combined with data from the Producers connected to other detector components to form a complete event data block. The combination is done by a EUDAQ Data Collector and data was stored in binary format. The stored data was saved to EOS, a CERN maintained disk-based storage service, for offline analysis.

#### 4.1.1 EUDAQ online data monitoring

Part of the EUDAQ framework were tools to monitor the data collection. Online analyses were developed to monitor in real time the stability of the pedestal values, noise and occupancies of each of the silicon sensor channels.

#### 4.1.2 Data unpacking and first analysis steps

The first step of the offline data analysis consisted of unpacking the CMS CE EUDAQ events. For this purpose a C++ library embedded in the EUDAQ framework has been developed.

An initial data quality check was performed before unpacking the raw data by comparing the difference in time-stamp with the time-stamp of the previous event as a check of the synchronisation for all the readout boards. During the October data taking only a few runs had events with a synchronization failure.

After this test the data were unpacked and the data from each ASIC were sorted into tables of 16-bit integers with the structure shown in figure 5 and stored in a ROOT [11] file. As zero-suppression was not used for simplicity, these tables contained the data from every channel of the ASICs, including those not connected to a detector channel. The data for each cell in an event contained data and pointer information from the 13 SCA cells for both the high- and the low-gain slow shapers, the ToA and the ToT measurements. The pointer was the address of first SCA cell data for the event, which allowed the ordering of the SCA data in time. This was required for the data reconstruction since the trigger was asynchronous with the 40 MHz clock. The data analysis workflow, which was developed in the CMSSW framework [12], used the ROOT files as input. It transformed the tables of 16-bit integers into a collection of calibrated hits.

#### 5 System synchronization

#### 5.1 Beam-characterization detectors

The tests of HGCAL and AHCAL prototypes with particle beams in the H2 area at CERN had been complemented by the readout of various beam-characterization detectors. Four delay wire chambers (DWC) [13] measured the trajectory and impact of the particles in the beam, two scintillator detectors served as external trigger source and two micro-channel plates (MCP) had been used to provide fast signals for reference timing measurement of the incident particles [14]. For this purpose, two 16-channel CAEN v1290N TDCs and one v1742 digitiser were integrated into the HGCAL prototype DAQ.

From each DWC four signals were separately discriminated at a threshold of -30 mV and fed as inputs to the TDC. Since the binning of the time-stamp digitization should be less than 1 ns corresponding to an optimal resolution of the position measurement of  $200 \mu \text{m}$  [13], a binning of 25 ps had been chosen. For proper event synchronization, the trigger for all CAEN modules stemmed from the duplicated TTL trigger signal issued by the sync board. After conversion to NIM, it was copied three times and fed into each CAEN module individually. After receiving a trigger from the sync board, events were built, were labeled with trigger time-stamps and subsequently stored in a local buffer.

Two dedicated EUDAQ producers [9] had been developed. They ran on a separate computer and communicated to these modules through optical link and VMEbus. These producers polled the event data from the buffers at a (configurable) frequency of 500 Hz (HGCAL DAQ rate  $\approx 40$  Hz), converted the raw data into the EUDAQ format and sent it to the main DAQ for storage and online data monitoring.

# 5.2 AHCAL

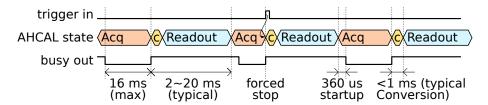

The front-end electronics of the AHCAL prototype were designed for low power operation under a specific ILC accelerator timing with a less than 1 ms long spill followed by 199 ms idle time. The operation of the Spiroc ASIC [15] was therefore split in 3 phases: 1) acquisition phase, where self-triggered events were stored into up to 16 analog memory columns; 2) conversion phase, where up to 16 events were sequentially digitized by internal ADC; 3) readout phase, where the digitized data was read out. Detailed timing was described in [16]. For beam test purposes, the acquisition phase length was extended to 16 ms, conversion phase took less than 1 ms and the readout phase varied typically between 2 to 20 ms, depending on the hit occupancy. Any external trigger from the sync board stopped the acquisition for immediate readout, as shown in figure 12.

Figure 12. The time diagram of AHCAL acquisition and readout phases.

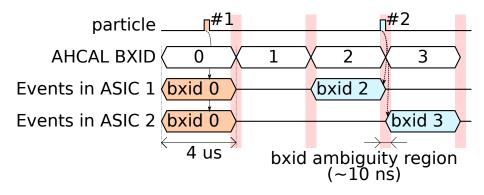

Due to the 'self-trigger' design of the ASIC, the AHCAL did not require an external trigger for data taking. All the hits (including noise hits) were read out and referenced by a number of bunch-crossing clock cycles (4  $\mu$ s period, called BXID) from the start of the acquisition phase. In order to assign an external trigger to the hits in the AHCAL, the external trigger number (with a time-stamp, 48-bit counter with a 25 ns resolution) and the time-stamp of the start of the relevant acquisition phase is internally sampled, as described in [16]. The trigger was assigned to one of the self-triggered events in the acquisition cycle. Assignment was based on the startup time from the start of the acquisition phase to the beginning of the first BXID and the additional delay due to the length of the trigger cable.

**Figure 13**. The organization of self-triggered particles in AHCAL BXIDs, showing the BXID ambiguity for an example of split events due to the time of arrival with respect to the BXID clock.

The collation of events according to the BXID might have however led to an existence of incomplete events for particles, that arrived close to the BXID counter value switching in the ASICs. An example for such a split event is shown in figure 13 (particle no. 2). Several factors contribute to the BXID ambiguity: time walk of the signals, clock skew due to board and ASIC location, clock tree distribution through the FPGAs and clock jitter. The internal ASIC TDC [15] had also a region of non-linearity around the BXID change. Therefore, particles arriving close to the BXID change, within 10 ns, needed to be excluded from the data analysis.

The AHCAL provided two means of synchronization with the HGCAL data: the trigger number and the trigger time-stamp, which used the 40 MHz clock from the HGCAL sync board. Both pieces of information were accessible in the data file.

#### 6 Collected data

The DAQ was operated at a readout rate of 40 Hz, limiting factor being the Raspberry Pi. At this rate the amount of data readout for a typical 5 second spill of the SPS for the HGCAL prototype was approx 300 MB, as each of the 94 silicon modules sent 16 KB of data per event.

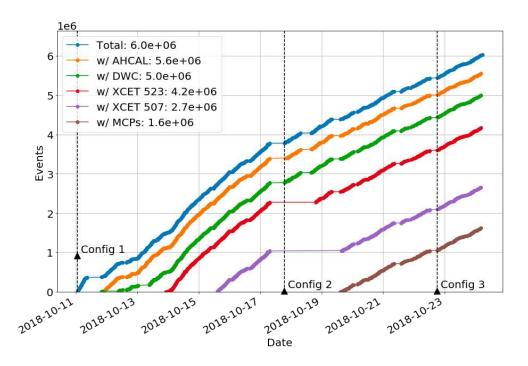

In the last run, over a period of two weeks, six million events were collected with beams of charged hadrons, electrons, and muons with momenta from 20 to 300 GeV/c, with different detector configurations. Figure 14 shows accumulated events for different detectors over the beam-test campaign.

# 7 Summary

In the upgrade of the CMS detector for when the HL-LHC is operational, the two endcap calorimeters will be replaced with high granularity sampling calorimeters equipped with silicon sensors. As part of the development of this calorimeter, a series of beam tests have been conducted with different sampling configurations using prototype segmented silicon detectors readout with a low-cost custom scalable data acquisition system. The software framework used for the run control and data collection was the portable modular EUDAQ framework. In the most recent of the tests conducted in late 2018 at the CERN SPS in 2018, the performance of a prototype calorimeter equipped with  $\approx 12,000$  channels of silicon sensors, in conjunction with the CALICE prototype analogue hadron calorimeter, was studied with beams of high-energy electrons, pions and muons, with six million events collected over a two week period.

Figure 14. The accumulated events for different detectors during beam-test campaign in October 2018.

#### Acknowledgments

We thank the technical and administrative staffs at CERN and at other CMS institutes for their contributions to the success of the CMS effort. We acknowledge the enduring support provided by the following funding agencies and laboratories: BMBWF and FWF (Austria); CERN; CAS, MoST, and NSFC (China); MSES and CSF (Croatia); CEA, CNRS/IN2P3 and P2IO LabEx (ANR-10-LABX-0038) (France); SRNSF (Georgia); BMBF, DFG, and HGF (Germany); GSRT (Greece); DAE and DST (India); MES (Latvia); MOE and UM (Malaysia); MOS (Montenegro); PAEC (Pakistan); FCT (Portugal); JINR (Dubna); MON, RosAtom, RAS, RFBR, and NRC KI (Russia); MoST (Taipei); ThEP Center, IPST, STAR, and NSTDA (Thailand); TUBITAK and TENMAK (Turkey); STFC (U.K.); and DOE (U.S.A.).

#### References

- D. Contardo, M. Klute, J. Mans, L. Silvestris and J. Butler, *Technical Proposal for the Phase-II Upgrade of the CMS Detector*, CERN-LHCC-2015-010 (2015) [LHCC-P-008] [CMS-TDR-15-02].

- [2] CMS collaboration, *The Phase-2 Upgrade of the CMS Endcap Calorimeter*, CERN-LHCC-2017-023 (2017) [CMS-TDR-019].

- [3] B. Acar et al., Construction and commissioning of CMS CE prototype silicon modules, 2021 JINST 16 T04002 [arXiv:2012.06336].

- [4] J. Borg et al., SKIROC2\_CMS an ASIC for testing CMS HGCAL, 2017 JINST 12 C02019.

- [5] F. Sefkow and F. Simon, *A highly granular SiPM-on-tile calorimeter prototype*, *J. Phys. Conf. Ser.* **1162** (2019) 012012 [arXiv:1808.09281].

- [6] M. Baber et al., Development and testing of an upgrade to the CMS level-1 calorimeter trigger, 2014 JINST 9 C01006.

- [7] C. Ghabrous Larrea et al., *IPbus: a flexible Ethernet-based control system for xTCA hardware*, 2015 JINST 10 C02019.

- [8] J. Mans and E. Frahm, Status report on a MicroTCA card for HCAL trigger and readout at SLHC, 2010 JINST 5 C12027.

- [9] EUDAQ Development Team, EUDAQ User Manual. Last update on October 2016 for EUDAQ version 1.7, (2016).

- [10] V. Brigljevic et al., Using XDAQ in application scenarios of the CMS experiment, eConf C 0303241

(2003) MOGT008 [FERMILAB-CONF-03-293] [CHEP-2003-MOGT008] [hep-ex/0305076].

- [11] https://root.cern.ch/guides/reference-guide.

- [12] https://twiki.cern.ch/twiki/bin/view/CMSPublic/WorkBookCMSSWFramework.

- [13] J. Spanggaard, Delay Wire Chambers A Users Guide, SL-Note-98-023-BI (1998).

- [14] N. Akchurin et al., *First beam tests of prototype silicon modules for the CMS High Granularity Endcap Calorimeter*, 2018 *JINST* **13** P10023.

- [15] S. Conforti Di Lorenzo et al., SPIROC: Design and performances of a dedicated very front-end electronics for an ILC Analog Hadronic CALorimeter (AHCAL) prototype with SiPM read-out, 2013 JINST 8 C01027.

- [16] J. Kvasnicka, Data Acquisition System for the CALICE AHCAL Calorimeter, 2017 JINST 12 C03043 [arXiv:1701.02232].